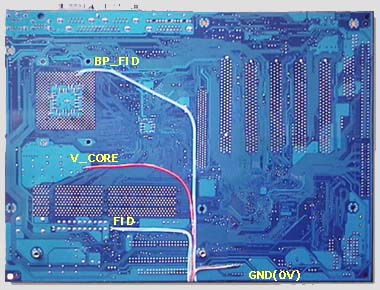

改造後のGA-7ZX-1の裏

この図ではV_COREをベタパターンからとっていますが、BP_FIDの隣のピンから取り出した方が作業が楽です。

FIDは電源コネクタの隙間を通して裏側に配線しました。

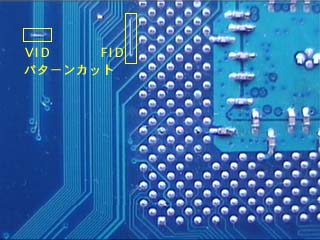

パターンカット

改造を途中で中止した場合もとに戻しやすいように

パターンカットは作業の最後にするようにします

パターンのカットは定規をあてて、カッターで20回も切れればいいくらいの気持ちで

力をいれすぎないよう、またあまり深く切らないようにします。

FIDパターンカット

VIDパターンカット

7ZX-HのページにVIDのパターンカットによらない切り離し方法を紹介しています。

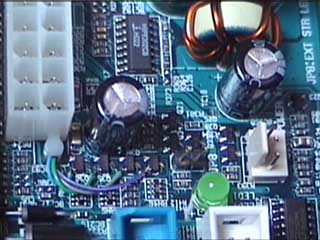

FID配線:Q35〜Q38

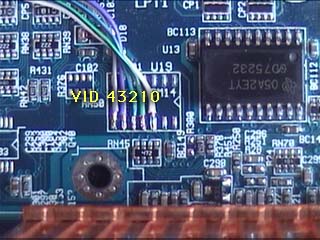

VID配線:U19 詳細

これは製作した基板の裏から見た配線図です。 ロータリーSWを4個を使用します。

各3bitでは不足するID設定用に、補助DIPスイッチをつけています。

配線図では6p-DIPになっていますが、製作には4p-DIPを使用しました。

そのためVID[0]の0.025V単位の設定を省略してGNDに落としました。

また設定を間違えたとき電源のショートを防ぐために、変則的ですがVcc_CORE側だけに電流制限抵抗を加えてあります。

起動倍率

補助DIPで設定範囲を決めます。

700-1050設定: DIP 1=off 2=off 3=on

500- 650 設定: DIP 1=on 2=on 3=off

1100以上の設定: DIP 1=on 2=on 3=off

次に表の通りロータリSWを設定します。

コア電圧

補助DIPで設定範囲を決めます。

1.5v以上は DIP 4=on

1.45以下は DIP 4=off

次に表の通りロータリSWを設定します。

Duron 700AST1Bを使ってテストした結果です。

定格コア電圧の1.5vで500Mhzから800Mhzまで

1.6vで850Mhz

1.75vで950Mhz

1.85vで1G

で動作することを確認できました。

温度(CPU):44°

温度(ケース):34°

電圧(Vcore):1.885 実測

|