Data

このページのすべてはDuronではSpitfire, AthlonではThunderbirdコアを対象にしています。

PalominoコアのMobile Athlon4, Athlon MP, Athlon XP 及び

MorganコアのDuron、Mobile Duronにはあてはまりません。

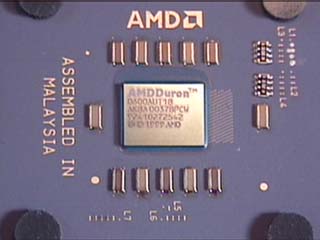

Duronの表面

右側にL1〜L4ブリッジと1Kオームの集積抵抗が見える。

下にあるのがL5〜L7ブリッジで、その他は、バイパスコンデンサ。

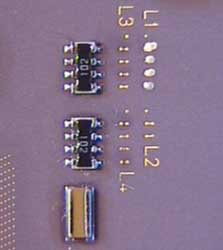

L1〜L4 [ Duron700 ]

L1ブリッジ[ ENABLE BP_FID ]

すべてクローズでBP_FID Pinが有効。

L3,L4ブリッジ[ BP_FID ]

このブリッジはCPUの起動倍率設定で、上から2個づつをペアとして使い、

ペア上側のブリッジを オープンにするとID横の倍率が有効となります。

このペアは、どちらか一方をオープンにした場合、必ずもう一方はクローズにします。

500〜1050Mhzの設定は 3x+有効倍率の合計

1100〜1250Mhzの設定は 11x+L3の有効倍率の合計

このときL4はID2,ID3 ともにペア上側のブリッジをクローズ(無効設定)にする

BP_FID 起動倍率設定 Duron/Athlon L3, L4

FID 設定 Duron/Athlon L6

L5〜L7 [ Duron700AST1B ]

L6ブリッジ [ FID ]

このブリッジは、ノースブリッジにFIDを渡すためのものです。

ブリッジを オープンにするとID横の倍率が有効となります。

500〜1050Mhzの設定は 3x+有効倍率の合計

1100〜1250Mhzの設定は 11x+L3の有効倍率の合計

このときID2,ID3 ともにブリッジをクローズ(無効設定)にします。

L7ブリッジ [ VID ]

ブリッジクローズでID横の電圧が有効となります。

コア電圧は有効電圧の合計+1.075v。

VID 電圧設定 Duron/Athlon L7

|